Applications

Flip-Chip

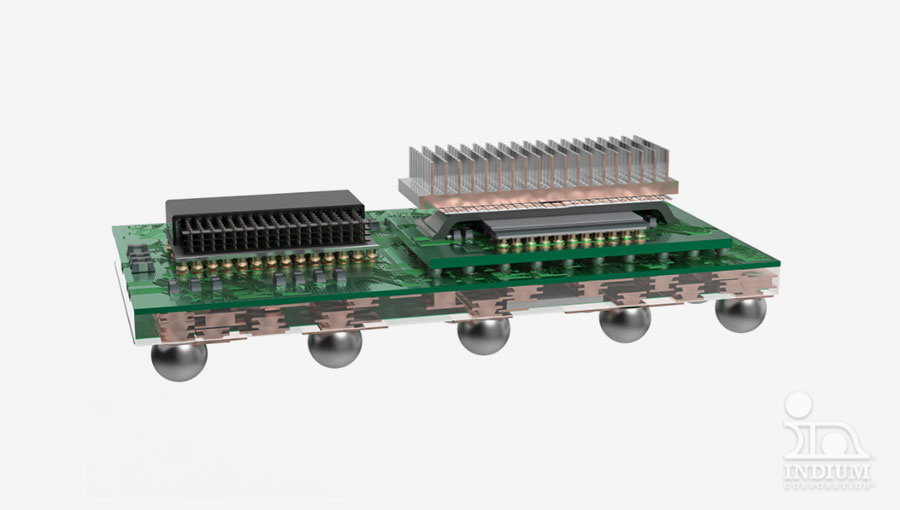

The flip-chip process involves removing individual dies from a wafer mounted on dicing tape, flipping them, and placing them onto a substrate. This substrate can be a printed circuit board, a lead frame, ceramic substrate, or, in the case of 2.5D and 3D assemblies, an interposer or wafer. As a leader in flip-chip flux chemistry, Indium Corporation pioneered the first ultra-low residue, no-clean flip chip flux over a decade ago, setting the standard for the industry.

Overview

Enabling Peak Performance in Increasingly Compact Advanced Packaging

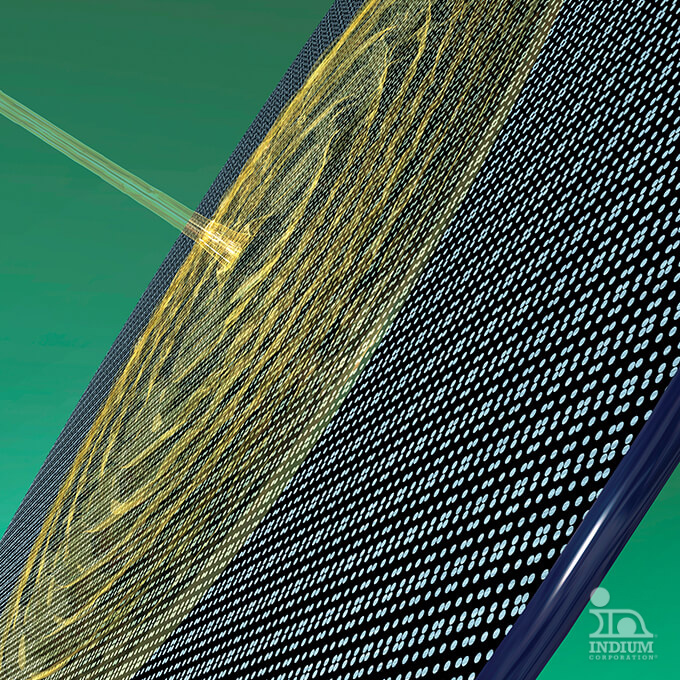

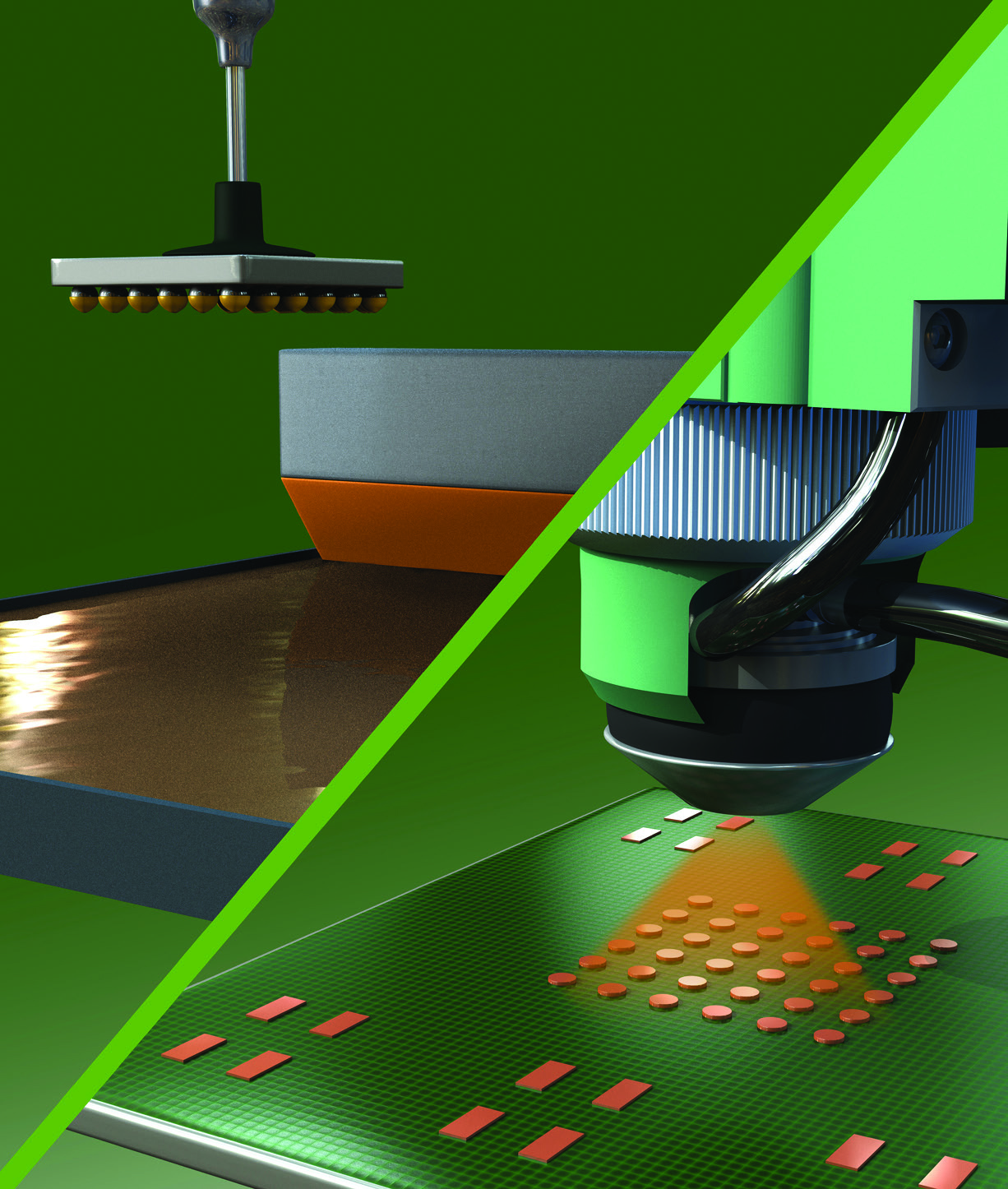

Flip-chip technology is widely used in advanced semiconductor packaging for high performance applications such as microprocessors, GPUs, and RF devices. This process typically involves placing a flipped die dipped with flux onto the substrate, or jetting flux onto the substrate before placing the flipped die, going through mass reflow, or thermos-compression bonding (TCB), or laser-assisted bonding (LAB), to form reliable solder joints for electrical and mechanical connection. This technique eliminates the need for wire-bonding, reducing signal path lengths, thus improving electrical and thermal performance.

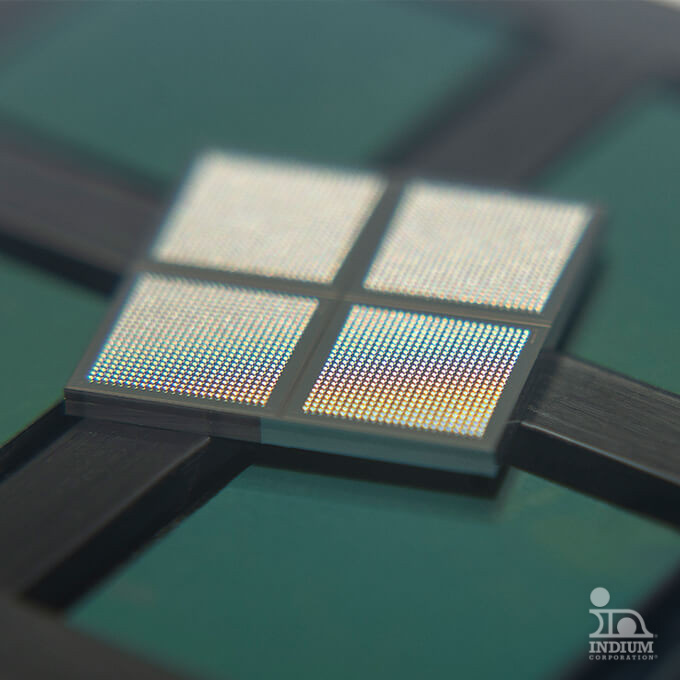

Flip-chip solder bumps have evolved to smaller solder microbumps and copper pillar in recent years, especially for the most advanced semiconductor platform. This shift gives rise to some challenges, such as efficiency in cleaning off flux residue under the tight spacing of flip chip die with high I/O counts, compatibility of flux residue with underfill material, open joints caused by warpage of this and large die, and etc., just to name a few. Our extensive range of flip chip fluxes, are tailored to address some of these challenges, such as ultra-low residue no clean fluxes like NC-809 and NC-26-A, easily cleanable water washable WS-641, and robust water washable WS-446HF.

Benefits

The Trusted Soldering Material Partner for High-Performance Flip-Chip Assembly

First

A decade ago, Indium Corporation introduced the first ultra-low residue flux and has since remained a pioneer in the field, offering a diverse range of ultra-low residue fluxes.

One Step

Our water-wash formula, WS-446HF, can be use for both ball-attach and flip-chip applications, making it more convenient to use a single flux for both processes.

Fluxless

Our fluxless tacking agent is designed for the formic acid reflow process in flip chip applications and is qualified for 2.5D applications.

Partnership

We collaborate closely with our customers and industry partners to create customized solutions that address their specific needs. Our experienced technical team offers consultation and support throughout the entire process, ensuring successful results every time.

Better Performance

Flip-chip packaging reduces the distance between the chips and the substrate, leading to lower inductance and resistance, which enhances signal integrity and reduces latency.

Improved Thermal Management

The direct connection to the substrate or heat spreader enhances heat dissipation, which is essential for high-performance applications.

Smaller Footprint

The flip-chip method enables high-density interconnections and smaller package sizes compared to traditional wire bonding, making it ideal for compact, high-performance devices.

Sustainability

These fluxes enable a true no-cleaning process, promoting sustainability by lowering costs related to cleaning chemicals, water, and energy consumption.

Related Applications

Related Markets

Your Success

is Our Goal

Optimize your processes with the latest materials, technology, and expert application support. It all starts by connecting with our team.