La fiabilité des interconnexions est essentielle pour la fiabilité de l'emballage des semi-conducteurs et des systèmes électroniques.

Si l'on considère le cycle de vie de la puce au système - de la conception du circuit intégré à l'assemblage de la carte et à l'intégration du système, en passant par la fabrication de la plaquette et l'emballage - l'élément commun est le "fil d'interconnexion" qui garantit la fiabilité du système électronique sur le terrain. L'objectif premier de l'emballage des semi-conducteurs est de générer des interconnexions entre la puce et le système à différents niveaux : de la puce au substrat, à la terminaison des composants, puis au circuit imprimé et au système, y compris diverses formes d'interconnexions, telles que les couches de redistribution (RDL), les trous de passage dans le silicium (TSV), le collage des fils, les joints de soudure, les bosses/boules, le collage direct au cuivre, et ainsi de suite. Il peut également s'agir de photonique (au lieu d'électronique). Au niveau du système, les interconnexions telles que les connecteurs, les fibres et les câbles jouent un rôle important dans la fiabilité du système électronique.

Essentiellement, l'emballage des semi-conducteurs crée des interconnexions le long de la chaîne de signaux, du circuit intégré au système, pour la distribution des signaux et de l'énergie. Au cours des six dernières décennies, l'emballage des semi-conducteurs a évolué avec la tendance générale à des interconnexions de plus en plus courtes. "Moins, c'est Moore" - La miniaturisation est bénéfique pour les performances, la puissance, la surface, le coût et la fiabilité(PPACR).

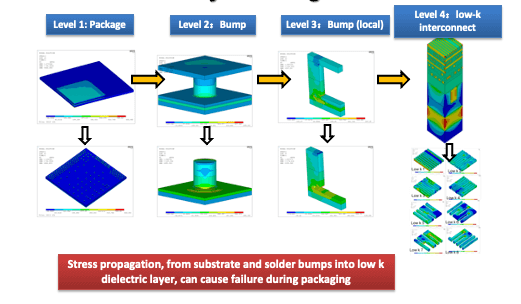

Pour assurer la fiabilité des interconnexions entre la puce et l'emballage, il faut d'abord prendre en compte les interactions entre la puce et l'emballage (CPI), car les diélectriques à faibledensité, utilisés pour les performances électriques de la puce, ont des propriétés mécaniques inférieures. Lorsque la puce passe par les différentes étapes de l'emballage, les contraintes mécaniques générées peuvent se propager à la puce, entraînant un désalignement, une déformation et une fracture du diélectrique. Pour gérer le problème de l'IPC, nous devons évaluer la propagation des contraintes du substrat et de la bosse de soudure dans la couche diélectrique de la puce, par le biais d'une modélisation multi-niveaux et multi-échelles (figure 1).

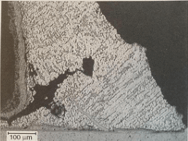

En ce qui concerne la fiabilité des interconnexions de soudure, nous devons tenir compte de diverses conditions de charge cyclique - telles que les cycles thermiques, qui entraînent une fatigue oligocyclique par le biais d'interactions fluage-fatigue, et les flexions et vibrations cycliques, qui entraînent une fatigue oligocyclique - qui provoquent des défaillances des joints de soudure par l'apparition et la propagation de fissures (figure 2). Nous devons également tenir compte des conditions de charge mécanique dynamique, telles que les chutes et les chocs mécaniques, qui peuvent entraîner une flexion à haute fréquence du substrat et la rupture du joint de soudure. Les facteurs importants à prendre en compte pour la fiabilité mécanique dynamique sont la dépendance à la vitesse de déformation, la concentration des contraintes et les matériaux intermétalliques interfaciaux (IMC).

Si les alliages sans plomb SAC (Sn/Ag/CU) peuvent répondre aux exigences de nombreuses applications, ils ne sont pas à la hauteur lorsqu'il s'agit de niveaux de contrainte élevés, car la vitesse de déformation par fluage du SAC augmente avec la contrainte et dépasse celle du SnPb à certains niveaux de contrainte élevés. Ces niveaux de contrainte élevés peuvent être dus à un décalage important du coefficient de dilatation thermique (CDT), à une large gamme de cycles thermiques, à une grande taille de composant ou à une faible hauteur de détachement. Pour plus de détails, voir le livre "Lead-Free Solder Interconnect Reliability" (Figure 3).

Dans ce contexte, un nouveau système de soudure a été développé avec une fiabilité accrue grâce au durcissement par précipitation et au durcissement en solution, et la pâte à braser a été formulée avec un taux de vide très faible. Il est considéré comme une solution de soudure "drop-in" car le processus de refusion est très similaire au processus SAC. Ce nouveau matériau a démontré une fiabilité supérieure en retardant l'apparition des fissures et en ralentissant leur propagation dans l'interconnexion des soudures pendant les cycles thermiques.

Souvent, une température de brasage basse peut être nécessaire pour réduire l'impact thermique sur les composants et pour réduire le gauchissement du substrat, qui peut causer de nombreux problèmes de qualité. Il arrive également qu'une brasure à basse température soit nécessaire pour un processus hiérarchique connu sous le nom de "soudure par étapes". Une soudure à basse température peut également contribuer à réduire la consommation d'énergie au cours du processus d'assemblage. Les alliages basse température existants (tels que le SnBi) se sont révélés peu performants lors des essais de chocs par chute en raison de leur fragilité. Un nouveau matériau a été mis au point pour la refusion à une température maximale de 200-210oC, avec des performances supérieures lors des cycles thermiques et des chocs mécaniques.

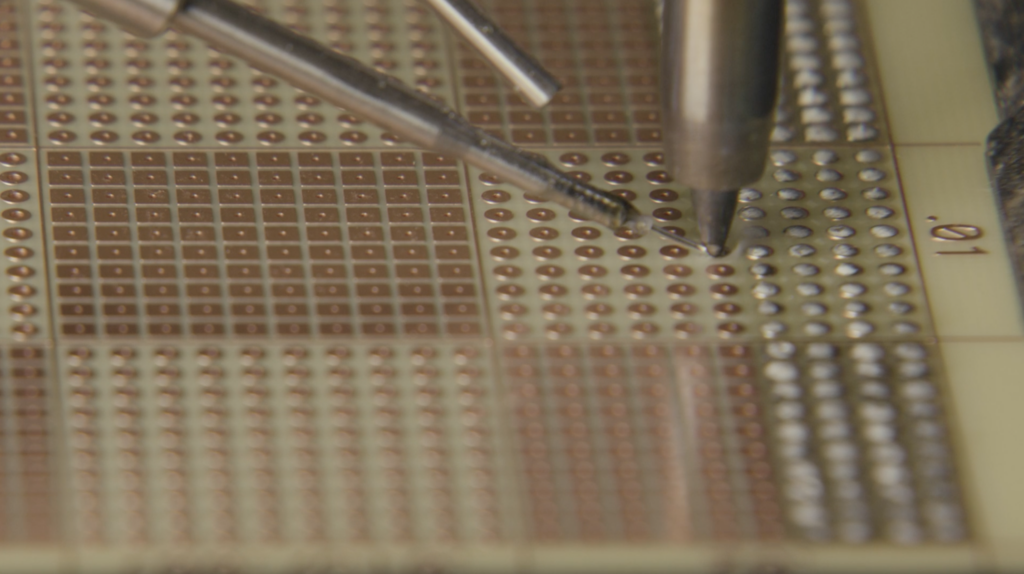

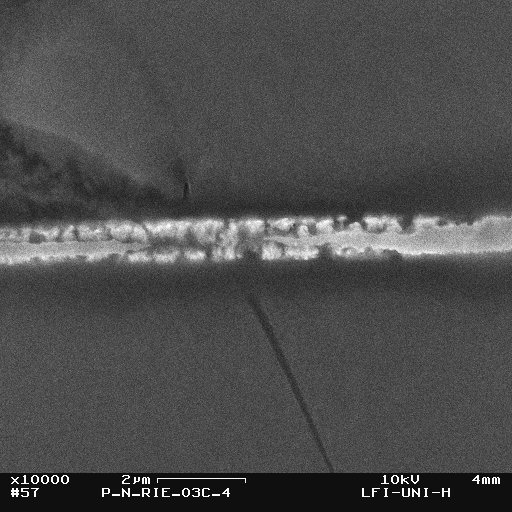

Outre la charge mécanique, la charge électrique peut également créer des problèmes de fiabilité des interconnexions. L'électromigration peut se produire sous l'effet d'un courant électrique et entraîner des défaillances de l'interconnexion (figure 4), et certains alliages de soudure (tels que le SnBi) sont connus pour être sujets à l'électromigration. Ce problème devient de plus en plus préoccupant à mesure que la densité du courant électrique augmente dans une interconnexion miniaturisée.

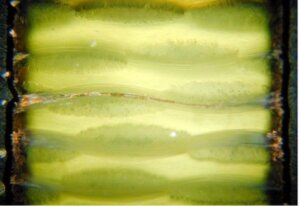

Parfois, les défaillances ne sont pas dues à l'absence d'une interconnexion voulue, mais à la présence d'une interconnexion non voulue. C'est le cas des chuchotements d'étain (figure 5), un filament spontané qui se développe très lentement mais qui peut provoquer une défaillance plusieurs années plus tard.

Une autre défaillance qui peut se produire est un filament anodique conducteur (CAF) dans un circuit imprimé ou un substrat, où un filament de cuivre (figure 6) se développe sous l'effet d'une polarisation électrique d'un via à un via voisin à travers l'espace entre la fibre de verre et la résine époxy avec la condensation de l'humidité. De même, les dendrites (figure 7) peuvent se développer par migration électrochimique en présence de résidus de flux (qui fournissent une contamination ionique) sous une polarisation électrique, provoquant ainsi un "court-circuit" dans un circuit électrique.

Alors que nous entrons dans l'ère de la 5G et de la 6G, l'impact des résidus de flux sur l'intégrité des signaux d'un circuit à haute fréquence est particulièrement intéressant. Les résidus de flux peuvent fournir un chemin alternatif aux signaux à haute fréquence (figure 8), et l'impact des résidus de flux sur l'intégrité des signaux est très sensible à la présence d'humidité. Ces considérations, ainsi que d'autres, conduisent au développement de formulations de flux sans nettoyage à ultra-faible résidu (ULR) qui sont adéquates pour le mouillage mais qui ont un impact très réduit sur le circuit, et qui sont également compatibles avec le moulage et l'underfill sans nettoyage.

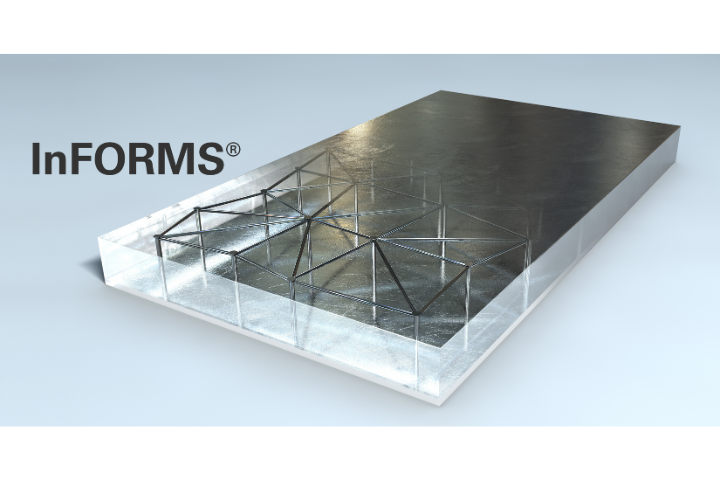

Un développement très intéressant pour les interconnexions à pas fin (inférieur à 10 µm) est l'interconnexion directe en cuivre, telle que le "collage hybride". Ce procédé offre une fiabilité d'interconnexion supérieure ainsi qu'une intégrité du signal grâce à une faible perte d'insertion due à un chemin d'interconnexion court.

Les produits électroniques devenant de plus en plus omniprésents dans les applications, la fiabilité des interconnexions doit être considérée de manière holistique en ce qui concerne les conditions environnementales (mécaniques et thermomécaniques, électriques et électrochimiques) qui donnent lieu à différents modes et mécanismes de défaillance. L'adoption croissante de l'intégration hétérogène entraîne une diversité accrue des interconnexions (avec des géométries, des matériaux et des interfaces différents) dans le même boîtier, ainsi que des modes et des mécanismes de défaillance complexes (et souvent interactifs). Ces considérations auront un impact sur l'ingénierie de la fiabilité des dispositifs à semi-conducteurs, y compris la conception, les matériaux, les processus et les essais.

Pour plus d'informations, veuillez contacter Dongkai Shangguan[email protected].(Vous trouverez plus de détails dans mon discours invité au 2022 IEEE Symposium on Reliability of Electronics Packaging & Photonics).