Die Zuverlässigkeit von Verbindungen ist entscheidend für die Zuverlässigkeit von Halbleitergehäusen und elektronischen Systemen.

Betrachtet man den Lebenszyklus vom Chip bis zum System - vom IC-Design über die Waferfertigung und das Packaging bis hin zur Leiterplattenmontage und Systemintegration - so ist das gemeinsame Element der "Verbindungsfaden" für die Zuverlässigkeit des elektronischen Systems im Feld. Der Hauptzweck des Halbleiter-Packaging ist die Herstellung von Verbindungen zwischen dem Chip und dem System auf verschiedenen Ebenen: vom Chip zum Substrat, zum Anschluss der Komponenten und dann zur Leiterplatte und zum System, einschließlich verschiedener Formen von Verbindungen, wie z. B. Umverteilungsschichten (RDL), Siliziumdurchkontaktierungen (TSV), Drahtverbindungen, Lötstellen, Bumps/Balls, direktes Cu-Bonden und so weiter. Sie kann auch durch Photonik (anstelle von Elektronik) erfolgen. Auf der Systemebene spielen Verbindungselemente wie Steckverbinder, Fasern und Kabel eine wichtige Rolle für die Zuverlässigkeit des elektronischen Systems.

Das Halbleiter-Packaging schafft im Wesentlichen Verbindungen entlang der Signalkette vom IC zum System für die Signal- und Leistungsverteilung. In den letzten sechs Jahrzehnten hat sich das Halbleiter-Packaging mit dem allgemeinen Trend zu immer kürzeren Verbindungen weiterentwickelt. "Less is Moore" - Miniaturisierung ist gut für Leistung, Stromverbrauch, Fläche, Kosten und Zuverlässigkeit(PPACR).

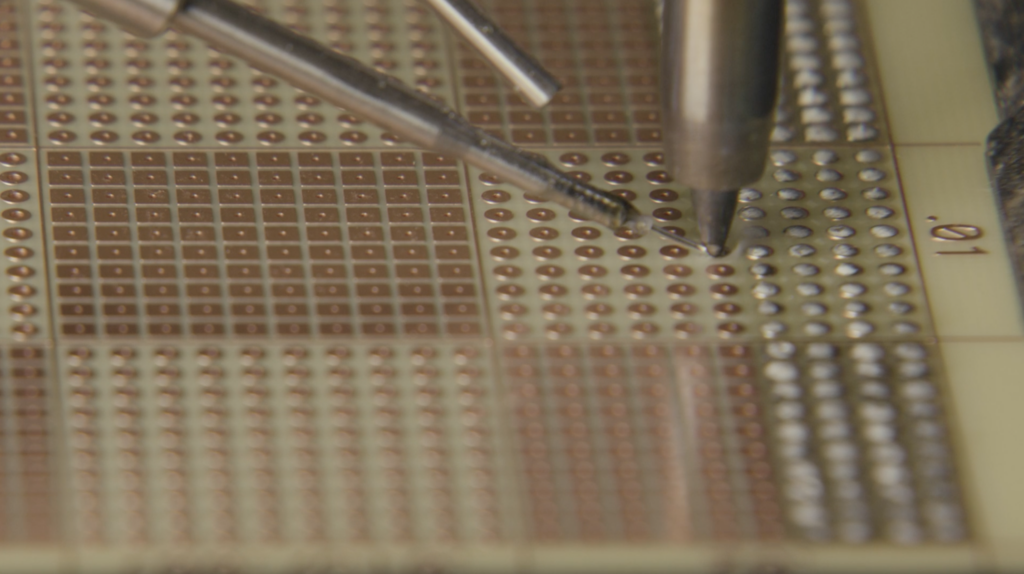

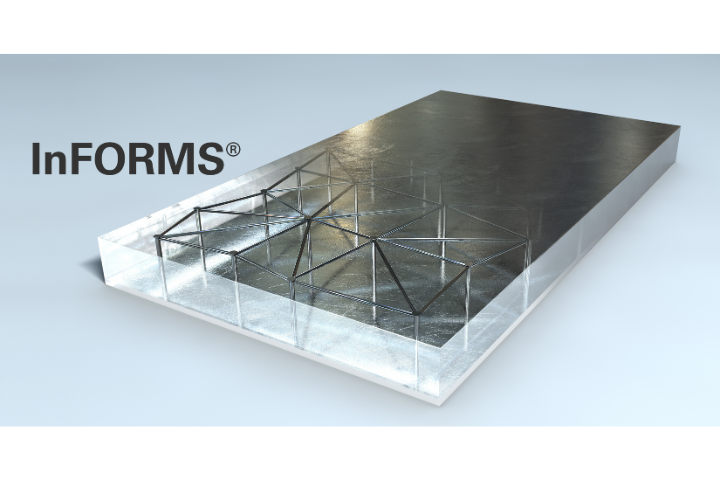

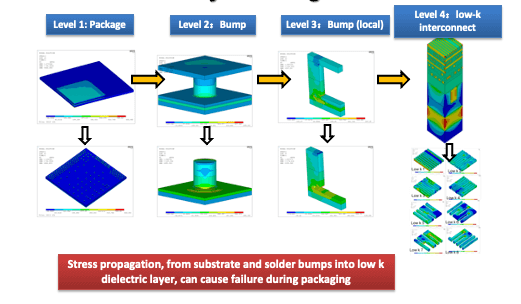

Um die Zuverlässigkeit der Verbindungen zwischen Chip und Gehäuse zu gewährleisten, müssen wir zunächst die Wechselwirkungen zwischen Chip und Gehäuse berücksichtigen, da die für die elektrische Leistung des Chips verwendeten Niederdielektrikaminderwertige mechanische Eigenschaften aufweisen. Wenn der Chip verschiedene Verpackungsschritte durchläuft, kann sich die erzeugte mechanische Spannung auf den Chip ausbreiten und eine Fehlausrichtung, Verformung und einen Bruch des Dielektrikums verursachen. Um das CPI-Problem in den Griff zu bekommen, müssen wir die Ausbreitung der Spannungen vom Substrat und der Lötstelle in die dielektrische Schicht des Chips durch eine mehrstufige, mehrstufige Modellierung bewerten (Abbildung 1).

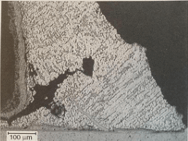

Für die Zuverlässigkeit von Lötverbindungen müssen wir verschiedene zyklische Belastungsbedingungen berücksichtigen, wie z. B. thermische Zyklen, die durch Kriech-Ermüdungs-Wechselwirkungen zu einer Ermüdung bei niedrigen Zyklen führen, sowie zyklische Biegungen und Vibrationen, die zu einer Ermüdung bei hohen Zyklen führen und Ausfälle von Lötverbindungen durch Rissbildung und -ausbreitung verursachen (Abbildung 2). Wir müssen auch dynamische mechanische Belastungsbedingungen wie Stürze und mechanische Stöße berücksichtigen, die eine hochfrequente Biegung des Substrats und einen Bruch der Lötstelle verursachen können. Zu den wichtigen Faktoren, die bei der dynamischen mechanischen Zuverlässigkeit zu berücksichtigen sind, gehören die Abhängigkeit von der Dehnungsrate, die Spannungskonzentration und die intermetallischen Grenzflächen (IMC).

Während die bleifreien SAC-Legierungen (Sn/Ag/CU) die Anforderungen vieler Anwendungen erfüllen können, sind sie bei hohen Belastungen unzureichend, da die Kriechdehnungsrate von SAC mit der Belastung zunimmt und die von SnPb bei bestimmten hohen Belastungen übersteigt. Diese hohen Spannungen können durch eine hohe Abweichung des thermischen Ausdehnungskoeffizienten (CTE), einen großen thermischen Zyklusbereich, eine große Bauteilgröße oder eine geringe Abstandshöhe entstehen. Weitere Einzelheiten sind in dem Buch "Lead-Free Solder Interconnect Reliability" zu finden (Abbildung 3).

Vor diesem Hintergrund wurde ein neues Lötsystem mit verbesserter Zuverlässigkeit durch Ausscheidungshärtung und Lösungshärtung entwickelt, und die Lötpaste wurde so formuliert, dass sie sehr wenig Lunker aufweist. Es wird als "Drop-in"-Lötlösung betrachtet, da der Reflow-Prozess dem SAC-Prozess sehr ähnlich ist. Dieses neue Material hat sich durch verzögerte Rissbildung und langsame Rissausbreitung in der Lötverbindung während der thermischen Wechselbeanspruchung als besonders zuverlässig erwiesen.

Häufig ist eine niedrige Löttemperatur erforderlich, um die thermischen Auswirkungen auf die Bauteile und den Verzug des Substrats zu verringern, der viele Qualitätsprobleme verursachen kann. Es gibt auch Situationen, in denen ein Niedrigtemperaturlot für ein hierarchisches Verfahren, das so genannte "Stufenlöten", benötigt wird. Ein Niedrigtemperaturlot kann auch dazu beitragen, den Energieverbrauch während des Montageprozesses zu senken. Bestehende Niedrigtemperaturlegierungen (wie SnBi) haben sich bei Fallschocktests aufgrund ihrer Sprödigkeit als schlecht erwiesen. Es wurde ein neues Material für das Reflow-Verfahren bei einer Spitzentemperatur von 200-210°C entwickelt, das bei Temperaturwechseln und mechanischen Stößen besser abschneidet.

Neben der mechanischen Belastung kann auch die elektrische Belastung zu Problemen bei der Zuverlässigkeit der Verbindungen führen. Elektromigration kann unter elektrischem Strom stattfinden und zu Verbindungsfehlern führen (Abbildung 4), und bestimmte Lötlegierungen (wie SnBi) sind bekanntermaßen anfällig für Elektromigration. Dies wird umso problematischer, je höher die elektrische Stromdichte in einer miniaturisierten Verbindung ist.

Manchmal kommt es zu Ausfällen, die nicht auf das Fehlen einer beabsichtigten Verbindung, sondern auf das Vorhandensein einer unbeabsichtigten Verbindung zurückzuführen sind. Ein solches Beispiel ist ein Zinnwhisker (Abbildung 5), ein spontaner Faden, der sehr langsam wächst, aber nach einigen Jahren zu einem Ausfall führen kann.

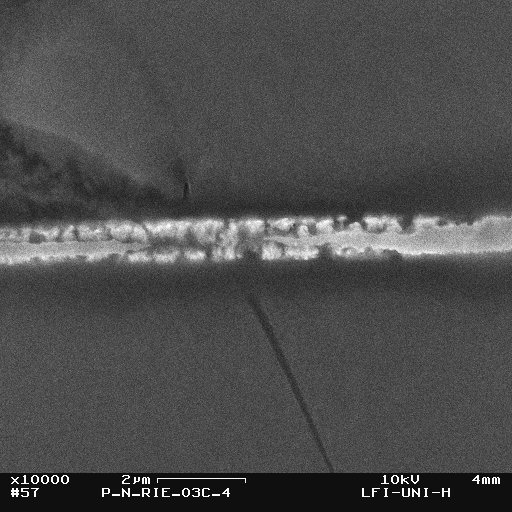

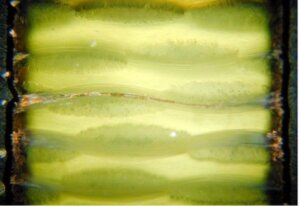

Ein weiterer Fehler, der auftreten kann, ist ein leitfähiger anodischer Faden (CAF) in einer Leiterplatte oder einem Substrat, bei dem ein Kupferfaden (Abbildung 6) unter elektrischer Vorspannung von einem Via zu einem benachbarten Via durch den Spalt zwischen der Glasfaser und dem Epoxidharz mit Feuchtigkeitskondensation wächst. In ähnlicher Weise können Dendriten (Abbildung 7) durch elektrochemische Migration in Gegenwart von Flussmittelrückständen (die für eine ionische Kontamination sorgen) unter einer elektrischen Vorspannung wachsen und so einen "Kurzschluss″ in einem Stromkreis verursachen.

Mit dem Eintritt in die Ära von 5G und 6G sind die Auswirkungen von Flussmittelrückständen auf die Signalintegrität eines Schaltkreises bei hohen Frequenzen von besonderem Interesse. Flussmittelrückstände können einen alternativen Pfad für Signale bei hohen Frequenzen darstellen (Abbildung 8), und die Auswirkungen der Flussmittelrückstände auf die Signalintegrität reagieren sehr empfindlich auf das Vorhandensein von Feuchtigkeit. Diese und andere Überlegungen treiben die Entwicklung von ULR-Flussmittelformulierungen (Ultra Low Residue) ohne Reinigung voran, die für die Benetzung geeignet sind, aber eine wesentlich geringere Auswirkung auf die Schaltung haben, und die auch mit dem Gießen und Underfill ohne Reinigung kompatibel sind.

Eine sehr interessante Entwicklung für Fine-Pitch-Verbindungen (unter 10 µm) ist die direkte Kupferverbindung, z. B. das "Hybrid Bonding". Dieses Verfahren bietet eine überragende Zuverlässigkeit der Verbindungen sowie eine hohe Signalintegrität aufgrund der geringen Einfügungsdämpfung durch einen kurzen Verbindungsweg.

Mit der zunehmenden Verbreitung elektronischer Produkte in den Anwendungen muss die Zuverlässigkeit der Verbindungen ganzheitlich betrachtet werden, und zwar im Hinblick auf die Umgebungsbedingungen - von den mechanischen und thermomechanischen bis hin zu den elektrischen und elektrochemischen Bedingungen -, die zu verschiedenen Ausfallarten und -mechanismen führen. Die zunehmende Einführung der heterogenen Integration führt zu einer größeren Vielfalt von Verbindungen (mit unterschiedlichen Geometrien, Materialien und Schnittstellen) im selben Gehäuse, zusammen mit komplexen (und oft interaktiven) Ausfallarten und -mechanismen. Diese Überlegungen werden sich auf die Zuverlässigkeitstechnik für Halbleiterbauelemente auswirken, einschließlich Design, Materialien, Prozesse und Tests.

Für weitere Informationen wenden Sie sich bitte an Dongkai Shangguan[email protected].(Weitere Einzelheiten finden Sie auch in meiner eingeladenen Keynote auf dem IEEE Symposium on Reliability of Electronics Packaging & Photonics 2022).