Das Advanced Packaging hat sich mit verschiedenen Verbindungstechnologien auf dem Weg zur heterogenen Integration weiterentwickelt. Verschiedene Montageverfahren werden eingesetzt, um die Ausbeute fortschrittlicher Gehäuse zu optimieren, während die Entwicklung innovativer fortschrittlicher Gehäusematerialien erforderlich ist, um die zahlreichen Herausforderungen zu bewältigen, die sich bei der Montage von System in Package (SiP) und miniaturisierten Modulen stellen.

Herausforderungen für moderne Verpackungsmaterialien

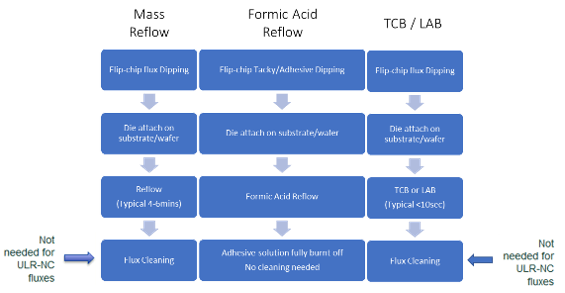

Größere Chips mit dicht gepackten Verbindungen - und den damit verbundenen engeren Abständen und kleineren Bumps - stellen den Montageprozess vor Herausforderungen, darunter verzugsbedingte offene Verbindungen und die Entfernung von Flussmittelrückständen aufgrund der engen Abstände. So stellt beispielsweise der Verzug eines größeren und dünneren Siliziumchips und eines dünnen Substrats zusammen mit einem asymmetrischen Bump-Design eine häufige Herausforderung dar, um eine gute Ausbeute beim Packaging zu erzielen. Thermokompressionsbonden (TCB), lasergestütztes Bonden (LAB) und Ameisensäure-Reflow ohne Flussmittel werden eingesetzt, um diese Herausforderungen zu meistern (Abbildung 1). Bei TCB- und LAB-Prozessen wird der Wafer oder das Substrat in der Regel über einen längeren Zeitraum auf einem beheizten Sockel bei 100-150 °C gehalten; wenn für den Bondprozess Flussmittel verwendet wird, kann dieser Zustand eine Herausforderung für die Reinigung der gehärteten Flussmittelrückstände darstellen.

Daher wurden neuartige Flussmittelformulierungen und Klebemittel für das Wafer/Die-Bonden entwickelt. Eine Lösung zur Bewältigung dieser Herausforderungen ist beispielsweise die Umstellung auf die Verwendung von Halbleiter-Flussmitteln mit ultrageringem Rückstand (ULR), die nicht gereinigt werden müssen, da die nach dem Lötprozess zurückbleibenden Flussmittelrückstände minimal sind (weniger als 10 %, sogar weniger als 1 %). Das ULR-Flussmittel wurde eingesetzt, um das Korrosionsrisiko zu beseitigen und gleichzeitig eine ausreichende Benetzung und Klebrigkeit zu gewährleisten, um gute Verbindungen zu bilden, ohne dass eine Reinigung erforderlich ist, da die minimalen Flussmittelrückstände mit den im anschließenden Prozess verwendeten Underfill- oder Formmaterialien kompatibel sind.

Beim Ameisensäure-Reflow ohne Flussmittel ("fluxless") wird ein klebriges Mittel verwendet, um den Chip während des Prozesses zu fixieren, und dieses klebrige Mittel sollte keine Rückstände hinterlassen, die mit dem nachfolgenden Prozess unverträglich wären.

Beim Fan-Out-Wafer-Level-Packaging (FOWLP) wird in der Regel ein Ball-Attach-Verfahren eingesetzt, um den Verbindungsbuckel zu bilden. Neben dem oben erwähnten Problem des Verzugs und der Wirksamkeit des Flussmittelentfernungsprozesses ist die Kompatibilität mit neuen dielektrischen Polymerbeschichtungen aus Polyimid, BCB und PBO ein weiteres Problemfeld. Delamination und Rückstände auf der dielektrischen Schicht sind einige der häufigsten Probleme aufgrund der Inkompatibilität zwischen den verschiedenen Materialien unter Temperatureinfluss. Nach einer gründlichen Untersuchung der Wechselwirkung zwischen dem Flussmittel und der dielektrischen Schicht bei verschiedenen Temperaturen wurden neue Flussmittel entwickelt, die mit den neuen dielektrischen Polymerbeschichtungen kompatibel sind.

Herausforderungen bei SiP

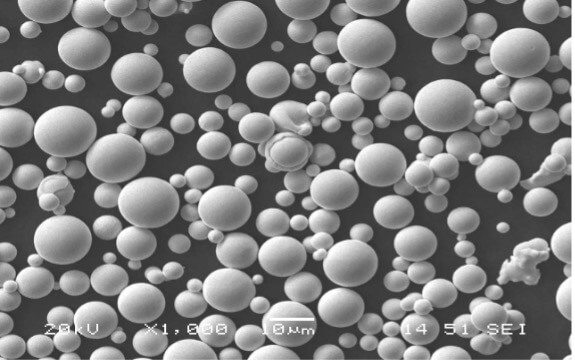

Die Abscheidung von Lotpaste für SiP-Anwendungen mit hoher Dichte ist zu einer großen Herausforderung geworden. Als Reaktion auf die Miniaturisierung und funktionale Verdichtung von Halbleitergehäusen für SiP und heterogene Integration wurde ein umfassendes Portfolio von Lotpasten für den Ultrafine-Pitch-Druck mit feinen Pulvern vom Typ 6 bis Typ 8 (Abbildung 2) entwickelt, um die Herausforderungen der Oxidation aufgrund der großen Oberfläche von feinen Pulvern zu bewältigen. Bei feinen Lötpastenanwendungen bis zu 100 µm oder weniger sind die Qualität des feinen Lötlegierungspulvers, die Flussmittelformulierung und die Rheologie der Lötpaste entscheidend für eine gleichmäßige Lötpastenabscheidung und eine gute Lötleistung. Diese wichtigen Merkmale tragen zur Verringerung von Lunkerbildung und Ablagerungen bei gleichbleibender Druckleistung bei und kombinieren eine hervorragende Benetzungsleistung mit einer exzellenten Schablonendruckübertragungseffizienz, um ein breites Spektrum an Prozessanforderungen zu erfüllen. Für bestimmte Verpackungsdesigns, bei denen der Druck von Lotpaste nicht möglich ist, können alternativ auch Mikrodosierung oder Präzisionsstrahlverfahren eingesetzt werden, die einen gleichmäßigen Auftrag bis zu einer Größe von 80µm ermöglichen.

Die Entwicklung neuer Lote ist ebenfalls ein entscheidender Faktor für die heterogene Integration. Legierungen mit unterschiedlichen Schmelztemperaturen können für SiP erforderlich sein, wenn verschiedene Reflow-Zyklen eine Lötmittelhierarchie erfordern. Darüber hinaus können Lote mit niedrigeren Schmelztemperaturen eine bessere Verzugskontrolle bieten, insbesondere bei dünnen Chips/Substraten, sowie eine minimale Wärmeeinwirkung auf wärmeempfindliche Komponenten. Legierungen mit erhöhter Zuverlässigkeit wurden auch für Automobilmodule und andere anspruchsvolle Anwendungen entwickelt.

Leistungselektronik und Wärmemanagement

Für die Leistungselektronik wurde eine Reihe von Materiallösungen entwickelt, darunter Low-Alpha-High-Pb-Lotpaste mit reduziertem Leckstrom für Hochleistungsbauelemente (z. B. GaN) und Durafuse™ HT (zum Patent angemeldet) unter Verwendung der Mischlotpulvertechnologie als Pb-freie Hochtemperaturalternative, die eine bessere Scherfestigkeit, Temperaturwechselbeständigkeit und Wärmeleitfähigkeit als (oder zumindest vergleichbar mit) High-Pb bietet und dabei ähnliche Lötverfahren wie das derzeitige High-Pb-Lötverfahren verwendet.

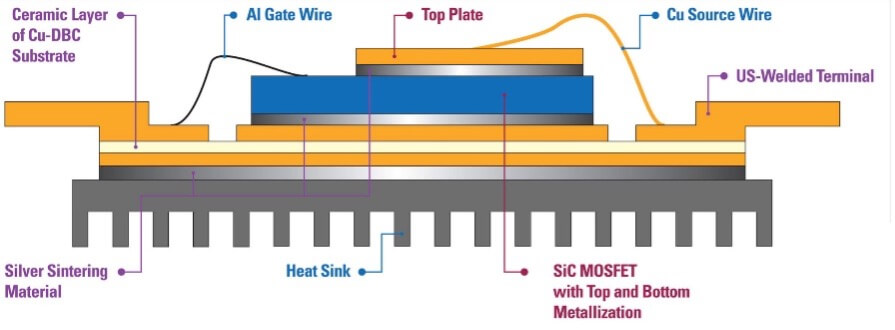

Die Entwicklung von Ag- und Cu-Sinterpastenformulierungen hat zu Lösungen für Die-Attach, Package-Attach und ähnliche Anwendungen in der Leistungselektronik geführt (Abbildung 3), die deutlich verbesserte Eigenschaften aufweisen, einschließlich der Scherfestigkeit der Verbindung und der Wärmeleitfähigkeit. Die hochmetallhaltigen Materialien sind so konzipiert, dass nach dem Sinterprozess nur minimale organische Rückstände zurückbleiben, wobei sie eine schnelle Sinterung und eine hohe Verbindungsfestigkeit bei druckloser und druckbeaufschlagter Sinterung auf verschiedenen Oberflächen (z. B. Ag, Cu und Au) aufweisen. Geringe Lunkerbildung und Porosität wurden mit vortrockenen und druckunterstützten Sinterverfahren erreicht.

Um die Herausforderungen des Wärmemanagements bei zunehmender Leistungsdichte von Halbleiterbauelementen und steigender Sperrschichttemperatur zu bewältigen, wurden im Laufe der Jahre mehrere Wärmeschnittstellenmaterialien (TIM) mit einem breiten Spektrum an Wärmeleitfähigkeit und Formen entwickelt. In anspruchsvollen Anwendungen werden zunehmend Metall-TIMs eingesetzt, darunter TIMs auf Indium- und Gallium-Basis. Interessant ist, dass Flüssigmetall-TIMs auf Galliumbasis aufgrund ihrer robusten Benetzungseigenschaften mit verschiedenen Oberflächen und dem Versprechen, "Leckagen" zu beseitigen, neue Möglichkeiten im Wärmemanagement eröffnen.