先進封裝持續演進,各種互連技術邁向異質整合。我們使用不同的組裝製程來優化先進封裝的良率,同時需要開發創新的先進封裝材料,以解決系統封裝 (SiP) 和微型模組在組裝製程中面臨的許多挑戰。

先進封裝材料面臨的挑戰

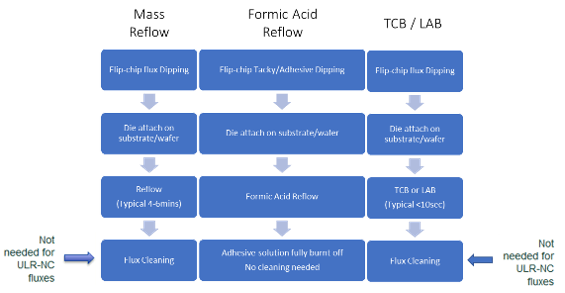

具有密集封裝互連元件的較大裸片尺寸 - 以及相關的較緊密間距和較小凸塊 - 在組裝製程中帶來了挑戰,包括翹曲引起的開放接點,以及由於間距緊密而導致的焊劑殘留清除挑戰等等。例如,更大更薄的矽晶片和更薄的基板所產生的翹曲,加上不對稱的凸塊設計,對於在封裝中達到良好的良率是一個常見的挑戰。熱壓接合 (TCB)、雷射輔助接合 (LAB) 和不含助熔劑的甲酸回流焊都可用來克服這些挑戰 (圖 1)。TCB 和 LAB 製程通常會將晶圓或基板放置在 100-150°C 的加熱基座上一段較長的時間;如果在接合製程中使用助焊劑,此狀況可能會對硬化的助焊劑殘留物造成清潔上的挑戰。

因此,用於晶圓/晶片接合的新型助焊劑配方和粘合劑已被開發出來。舉例來說,轉向使用半導體級超低殘留 (ULR) 免清洗倒裝晶片助焊劑是克服這些挑戰的解決方案之一,因為焊接製程後留下的助焊劑殘留物極少 (少於 10%,低至 1%)。利用 ULR 助焊劑消除了腐蝕風險,同時提供足夠的潤濕性和粘性,形成良好的接點而無需清洗,因為極少的助焊劑殘留與後續製程中使用的底部填充或成型材料相容。

對於不使用助焊劑的甲酸回流焊 (「無助焊劑」),在製程中會使用粘性或黏性劑來固定裸片,此粘性劑不應產生任何與後續製程不相容的殘留物。

對於扇出式晶圓級封裝 (FOWLP),通常會採用球型吸附製程來形成互連凸塊。除了上述的翹曲問題和除焊劑製程的有效性之外,與聚醯亞胺、BCB 和 PBO 等新型介電聚合物塗層的相容性也是另一個值得關注的問題。由於不同材料在溫度影響下的不相容性,介電層上的分層和殘留物是一些常見的問題。在徹底研究助焊劑材料與介質層在不同溫度下的互動關係後,已開發出與新型介質聚合物塗層相容的新型助焊劑材料。

SiP 的挑戰

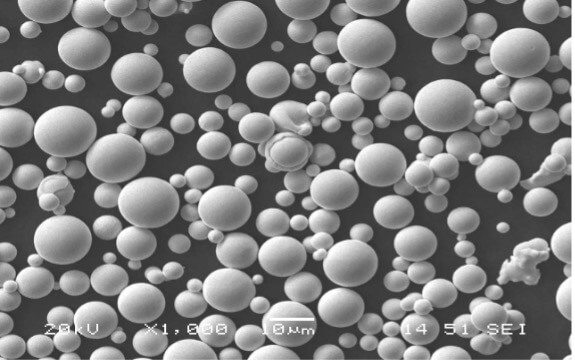

高密度 SiP 應用的焊膏鍍膜已變得非常具有挑戰性。為了因應 SiP 和異質整合半導體封裝的微型化和功能密集化,透過克服由於精細粉末的大表面面積所造成的氧化挑戰,已開發出專為超精細間距印刷而設計的全面性焊膏產品組合,其精細粉末範圍從 Type 6 到 Type 8 (圖 2)。對於低至 100µm 或更小的微細焊膏應用,微細焊料合金粉末的品質、助焊剂配方和焊膏流變對於實現一致的焊膏沉積和良好的焊接性能至關重要。這些重要的特性有助於以一致的印刷性能減少空泡和坍塌,結合優異的潤濕性能和出色的鋼版印刷轉印效率,滿足最廣泛的工藝要求。對於某些可能無法印刷焊膏的封裝設計,也可以使用微點膠或精密噴射來作為替代方案,其穩定的沉積可達 80µm 的特徵尺寸。

新焊料的開發也是異質整合的重要推動力。當有不同的回流週期需要焊料層次時,SiP 可能需要不同熔化溫度的合金。此外,較低熔解溫度的焊料可提供較佳的翹曲控制,尤其是對於薄型晶粒/基板而言,並可將熱敏元件的受熱程度降至最低。此外,還針對汽車模組和其他要求嚴苛的應用,開發出具有更高可靠性的合金。

電力電子與熱能管理

我們已針對功率電子產品開發出一系列材料解決方案,包括適用於高功率元件 (如 GaN) 且可降低漏電流的低 Alpha 高 Pb 焊膏,以及使用混合焊粉技術的 Durafuse™ HT (專利申請中) 作為高溫無 Pb 替換品,其接合剪切強度、熱循環可靠性和熱導率均優於 (或至少與) 高 Pb,同時使用與目前高 Pb 焊接製程類似的焊接製程。

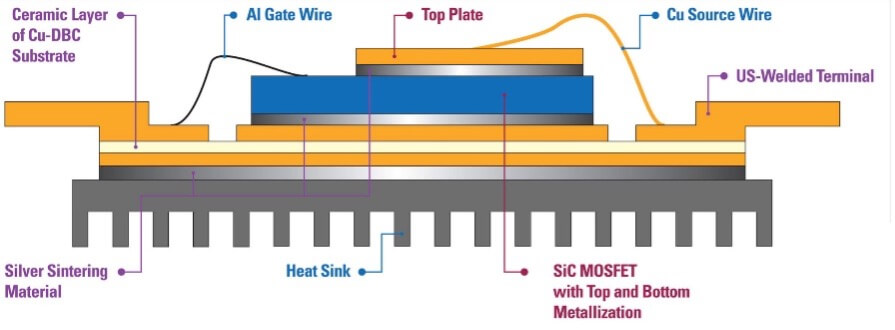

銀和銅燒結漿料配方的發展,為功率電子的晶粒貼合、封裝貼合和類似應用提供了解決方案(圖 3),並顯著增強了特性,包括接合剪切強度和熱導率。高金屬負載材料的設計目的是在燒結製程後留下最少的有機殘留物,在不同的表面處理(如銀、銅和金)上,無壓和加壓燒結速度快,接合強度高。預乾燥和加壓輔助燒結製程已達到低空隙和低孔隙率。

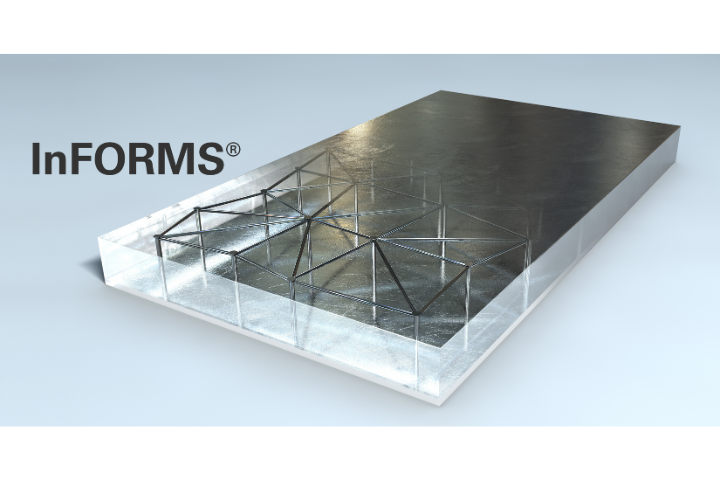

為了因應半導體元件功率密度增加及結點溫度上升所帶來的熱能管理挑戰,多年來已開發出多種不同熱傳導率及形式的熱介面材料 (TIM) 解決方案。金屬 TIM 越來越多地被用於要求嚴苛的應用中,包括铟基 TIM 和鎵基 TIM。值得注意的是,鎵基液態金屬 TIM 因其與各種表面的強韌濕潤特性,以及消除 「洩漏 」的承諾,正在為熱管理開拓新的可能性。