互連可靠性對半導體封裝和電子系統的可靠性至關重要。

如果我們從晶片到系統的生命週期來看 - 從 IC 設計、晶圓製造、封裝到電路板組裝和系統整合 - 共同的元素就是電子系統在現場可靠性的「互連線路」。半導體封裝的主要目的是在不同層級產生從晶片到系統的互連:從晶片到基板,到元件端接,再到 PCB 和系統,包括各種形式的互連,如再分布層 (RDL)、通矽通孔 (TSV)、導線接合、焊點、凸點/球、直接銅焊等。也可以透過光子學 (而非電子)。在系統層級,連接器、光纖和電纜等互連元件在電子系統的可靠性方面扮演重要角色。

基本上,半導體封裝是在從 IC 到系統的信號鏈上建立互連,以進行信號和電源分配。在過去的六十年間,半導體封裝隨著互連不斷縮短的整體趨勢而發展。「少就是摩爾」-微型化對效能、功耗、面積、成本和可靠性(PPACR) 都有好處。

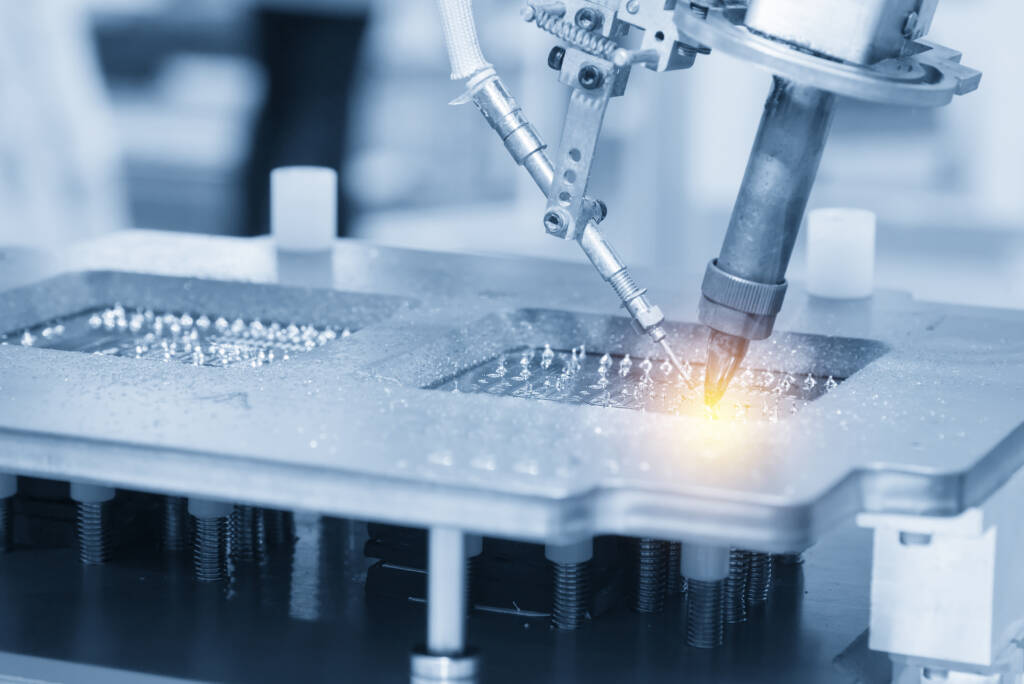

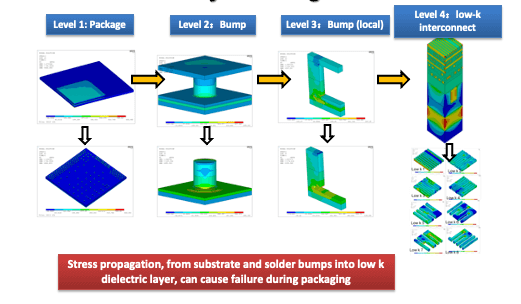

對於從晶片到封裝的互連可靠性,我們需要首先考慮晶片封裝互動 (CPI),因為用於晶片電氣性能的低介電質具有較差的機械特性。當晶片經過各種封裝步驟時,所產生的機械應力可能會傳播至晶片,造成錯位、變形和介電體破裂。為了處理 CPI 問題,我們需要透過多層次多尺度的建模(圖 1)來評估應力從基板和焊接凸塊傳播到晶片中介電層的情況。

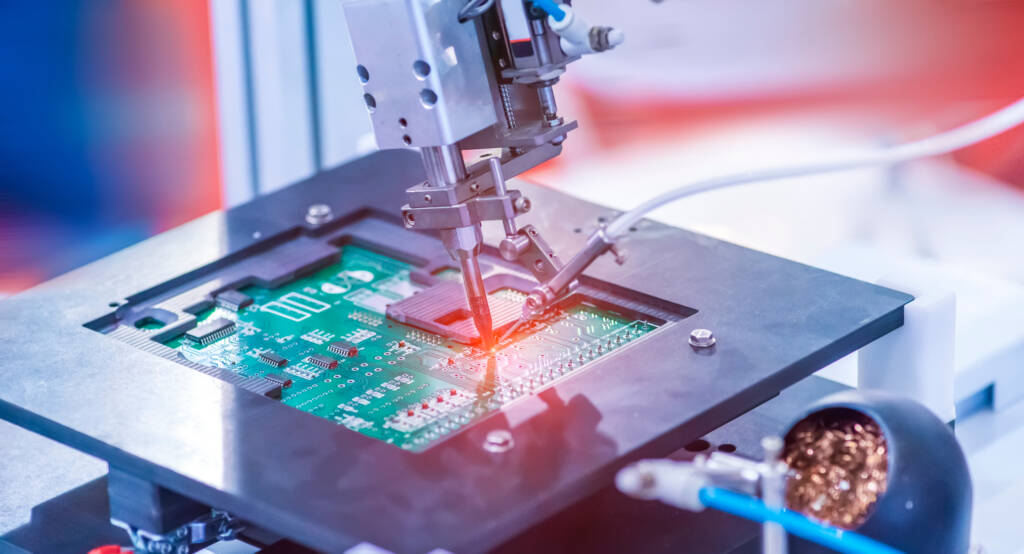

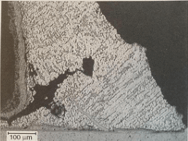

對於焊料互連的可靠性,我們需要研究各種循環負載條件 - 例如熱循環,它會透過蠕變-疲勞互動作用導致低循環疲勞,以及循環彎曲和振動,它會導致高循環疲勞 - 透過裂縫的產生和擴散造成焊點故障(圖 2)。我們也需要考慮動態機械負載條件,例如跌落和機械衝擊,這會造成基板的高頻率彎曲和焊點的破裂。動態機械可靠性需要考慮的重要因素包括應變率依賴性、應力集中和介面金屬間化合物 (IMC)。

雖然無鉛 SAC (Sn/Ag/CU) 合金可以滿足許多應用的需求,但在高應力層級上卻有不足,因為 SAC 的蠕變應變率會隨著應力而增加,在某些高應力層級上會超過 SnPb 的蠕變應變率。這些高應力等級可能是由於高熱膨脹係數 (CTE) 不匹配、大的熱循環範圍、大的元件尺寸或低的stand-off 高度所造成。更多詳細資訊可參閱「無鉛焊料互連可靠性」一書 (圖 3)。

在此背景下,新的焊料系統已經開發出來,透過沉澱硬化和溶液硬化提高了可靠性,而且焊膏的配方具有非常低的空泡率。由於回流焊製程與 SAC 製程非常相似,因此它被視為一種「drop-in」焊料解決方案。這種新材料在熱循環過程中延遲了裂紋的產生,並減緩了裂紋在焊料互連中的擴散,因此展現出優異的可靠性能。

通常,可能需要較低的焊接溫度,以降低對元件的熱影響,並減少可能導致許多品質問題的基板翹曲。在某些情況下,也需要使用低溫焊料來進行稱為 "step soldering" 的分層製程。低溫焊料也有助於降低組裝過程中的能源消耗。現有的低溫合金(例如 SnBi)在跌落衝擊測試中因為脆性而表現不佳。目前已開發出一種新材料,適用於峰值溫度為200-210oC的回流焊,在熱循環及機械衝擊下具有優異的性能。

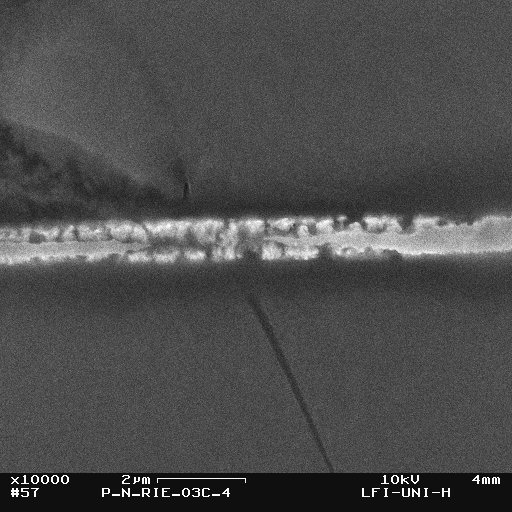

除了機械負載之外,電氣負載也會造成互連可靠性問題。電遷移會在電流下發生,導致互連故障 (圖 4),而某些焊料合金 (例如 SnBi) 是已知容易發生電遷移的材料。隨著微型化互連中電流密度的增加,這一問題變得更加令人關注。

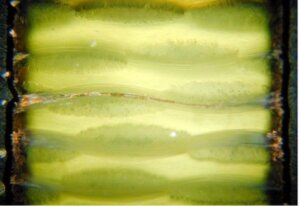

有時候,故障的發生不是因為沒有預期的互連,而是因為出現了非預期的互連。其中一個例子就是錫縫 (圖 5),它是一種自發形成的絲狀物,生長速度非常緩慢,但卻可能在數年後造成故障。

另一種可能發生的故障是 PCB 或基板中的導電陽極銅絲 (CAF),銅絲 (圖 6)會在電偏壓下從一個通孔長到鄰近的通孔,通過玻璃纖維與環氧樹脂之間的縫隙,並伴有濕氣凝結。同樣地,樹枝狀突起 (圖 7)也會在電氣偏壓下,透過電化學遷移,在有助焊剂殘留物 (提供離子污染) 的情況下生長,進而造成電路「短路」。

隨著我們進入 5G 和 6G 時代,磁通殘渣對高頻電路信號完整性的影響尤其值得關注。磁通殘渣可在高頻率下提供訊號的替代路徑 (圖 8),而磁通殘渣對訊號完整性的影響對濕氣的存在非常敏感。這一點以及其他考慮因素正推動著超低殘留 (ULR) 免清洗助焊劑配方的發展,這些配方具有足夠的濕潤性,但對電路的影響卻大大降低,而且這些配方還與無需清洗的成型和底部填充相容。

對於細間距互連 (10 微米以下) 來說,一個非常令人振奮的發展是直接銅互連,例如「混合接合」。由於互連路徑較短,插入損耗較低,因此此製程可提供優異的互連可靠性以及訊號完整性。

隨著電子產品的應用越來越廣泛,互連可靠性必須從整體考慮環境條件 - 從機械和熱機械,到電氣和電化學 - 這些環境條件會產生不同的失效模式和機制。隨著異質整合的日益普及,同一封裝中的互連元件 (具有不同的幾何形狀、材料和介面) 的多樣性也隨之增加,同時也產生了複雜 (且經常是互動的) 可靠性失效模式和機制。這些考慮因素將影響半導體裝置的可靠性工程,包括設計、材料、製程和測試。

如需更多資訊,請聯絡上官東凱[email protected]。(更多詳細資訊也可參閱我在 2022 年 IEEE 電子封裝與光子學可靠性研討會的受邀主題演講)。