Das Wärmemanagementwird zu einer immer wichtigeren Herausforderung für Halbleiterbauelemente, da die Funktions- und Leistungsdichte zunimmt - insbesondere bei fortschrittlichem Packaging. Thermische Testchips (TTC) sind eine wichtige Voraussetzung für die Entwicklung von Wärmemanagementlösungen für Hochleistungs-Halbleitergeräte.

Wie werden TTCs hergestellt?

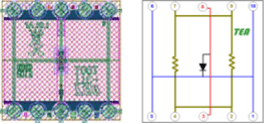

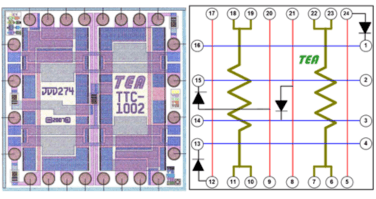

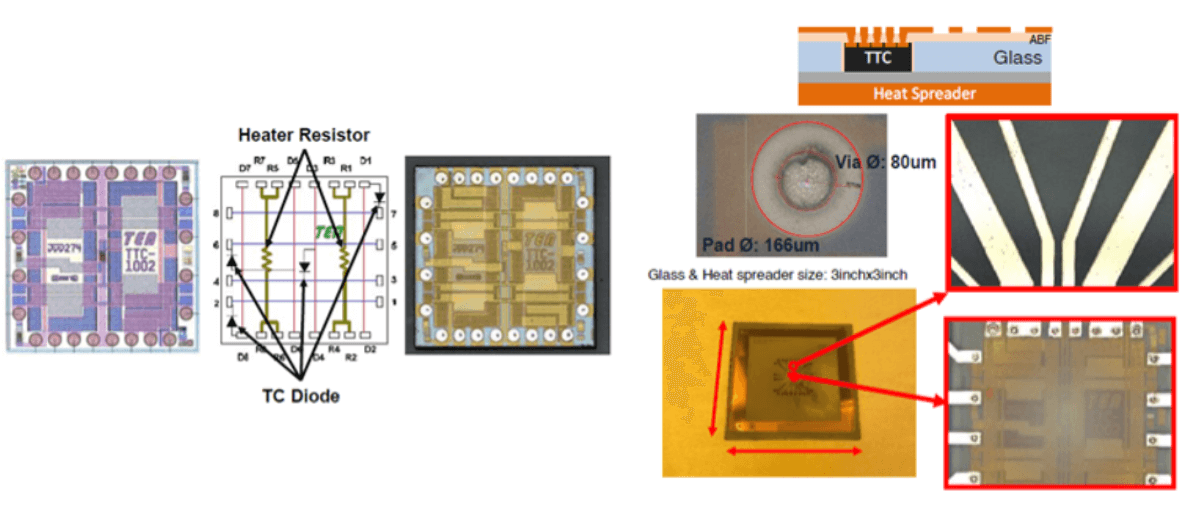

TTCs aus in Amerika hergestellten Siliziumwafern (Abbildung 1) können die Größe und die ungleichmäßige Leistungsverteilung (z. B. Hot Spots) eines realen Halbleiterchips genau simulieren und verfügen über eingebettete On-Chip-Sensoren zur Echtzeit-Temperaturmessung des Chips. Der TTC, ein analoger ASIC, besteht aus Einheitszellen (Abbildungen 2 und 3), wobei die Leistungsaufnahme und die Temperatur jeder Einheitszelledirekt adressierbar sind, so dass eine konfigurierbare Leistungsverteilung und eine In-situ-Temperaturmessung auf dem Chip möglich sind - bis hin zum Maßstab einer Einheitszelle.

Für die Wärmequelle in der Einheitszelle werden Metallfilmwiderstände verwendet, um eine bessere Gleichmäßigkeit und Anpassung über den Wafer zu erreichen, und ihre relativ stabilen Temperaturkoeffizienten führen zu einer konstanten Verlustleistung im Verlauf der thermischen Messung. Die Wärmequellen sind außerdem so ausgelegt, dass sie der JEDEC-Norm JESD51-4 entsprechen. Strategisch im TTC angeordnete Temperaturmessdioden (TSD) ermöglichen eine präzise Messung der Temperatur des Chips an mehreren Stellen gleichzeitig.

Da die Einheitszellen in beliebiger Kombination angeordnet werden können, kann der TTC beliebig groß sein, um der Größe des realen Chips zu entsprechen (bis zu 50 mm x 50 mm oder größer, falls erforderlich). Das TTC mit seiner Präzision und Genauigkeit der integrierten Heizelemente und Sensoren in jeder Einheitszelle kann das thermische Verhalten eines realen Halbleiterchips genau simulieren und bietet damit ein hervorragendes Werkzeug für die gleichzeitige Entwicklung von Wärmemanagementlösungen während der Entwicklung eines neuen Chips (was oft mehrere Jahre dauert).

Verwendung von thermischen Testchips für den Bau von Testfahrzeugen

Mit den TTCs (die für das Drahtbonden oder die Flip-Chip-Befestigung ausgelegt sind) können thermische Testfahrzeuge (TTV) in verschiedenen Gehäuseformaten wie BGA, LGA, COB usw. sowie mit mehreren Chips pro Gehäuse (Abbildung 4) entwickelt werden, um System-in-Package (SiP) zu simulieren, das häufig bei der heterogenen Integration verwendet wird.

Durch die Möglichkeit der konfigurierbaren Leistungsverteilung und der gleichzeitigen Temperaturmessung auf dem Chip können TTCs und TTVs sehr nützlich für die thermische Charakterisierung (stationär und instationär) und Bewertung sein, einschließlich der Abbildung von Leistung und/oder Temperatur bei Halbleitergehäusen und -geräten, die verschiedene Lösungen für das Wärmemanagement enthalten können - Wärmeschnittstellenmaterialien (TIM), Kühlkörper, Dampfkammer, Wärmerohr, Kühlplatte, Flüssigkeitskühlung usw. Sie können auch sehr nützlich für die Validierung von thermischen Simulationen und Modellen sein. Außerdem können Leistungszyklen in einer programmierten Umgebung durchgeführt werden, um die Zuverlässigkeit verschiedener Wärmemanagementlösungen zu bewerten.

Thermische Testchips für Glas-Interposer: Eine Fallstudie

In der Tat können TTCs auch den Anforderungen des Advanced Packaging gerecht werden. In einem aktuellen Forschungsprojekt, das auf der 73. IEEE-Konferenz für elektronische Bauteile und Technologie (ECTC) 2023 in Orlando, FL, in einem Beitrag mit dem Titel"Bottom Side Cooling for Glass Interposer with Chip Embedding using Double-sided Release Process for 6G Wireless Applications" (Unterseitenkühlung für Glas-Interposer mit Chip-Embedding unter Verwendung eines doppelseitigen Freigabeprozesses für 6G Wireless-Anwendungen) vorgestellt wurde, verwendeten Forscher der Georgia Tech und der Penn State University TTCs von Thermal Engineering Associates (TEA) für die Entwicklung eines Glas-Interposer-Prozesses mit Chip-Embedding (Abbildung 5). Bei dem Glas-Interposer werden in das Glassubstrat Durchgangshohlräume eingebracht, der TTC wird in den Durchgangshohlraum eingebettet und über Umverteilungsschichten (RDL) auf der Oberseite angeschlossen. Ein Kupfer-Wärmespreizer ist an der exponierten TTC-Rückseite mit einer TIM-Schnittstelle für das Wärmemanagement angebracht. Die Leistungsdichte des eingebetteten TTC wird getestet, um die Kühlkapazität mit verschiedenen Wärmeübergangskoeffizienten zwischen 28,8 und 261,3 W/m2Kzu ermitteln.

Insgesamt werden TTCs und TTVs in der Lage sein, Halbleiterchips und fortschrittliche Gehäuse in ihrer Entwicklung eng zu emulieren - mit zunehmender Leistungsdichte und komplexeren Gehäusekonfigurationen. TTCs in Form von gestapelten Chips und Chiplets in 2,5D/3D-Gehäusen befinden sich derzeit in der Entwicklung.